Empowering Better SoC Design

Our Customers and Partners

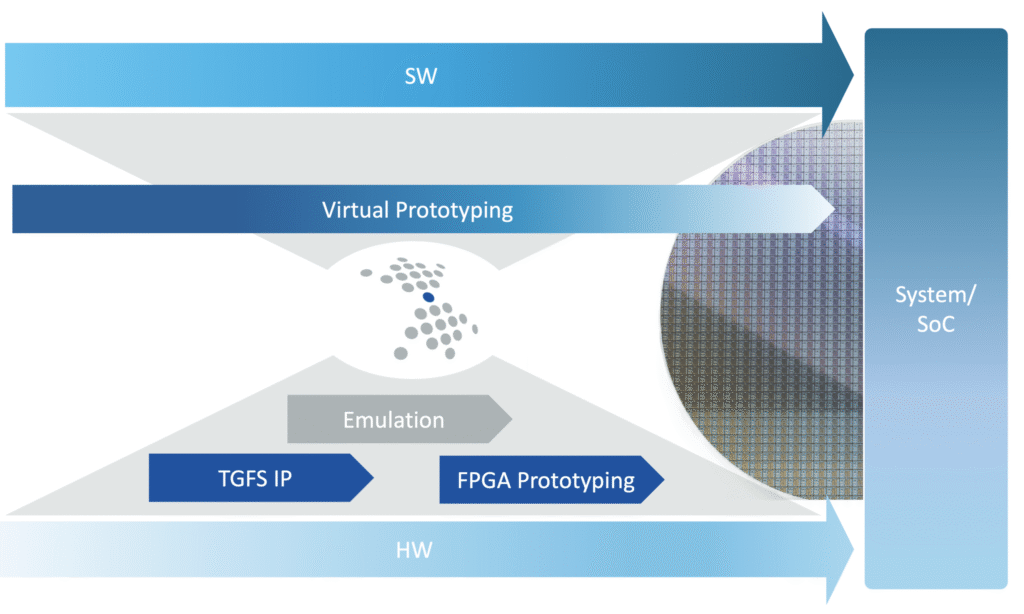

Our Approach

System-on-Chip and embedded system design is complex.

We make it easier by helping you to design better.

The MINRES approach is to introduce tried, tested and trusted design methodology, productivity IP, tools and design IP to solve your design challenges, while improving your software-driven design processes, and even training your teams.

Your design team is enabled with more productive design processes and empowered to turn great ideas into market-leading innovative products faster and more dependably.

Our silicon-proven, EDA tools-agnostic productivity and design IP provide you with high levels of abstraction and seamless integration.

Our deep understanding of safety and security requirements is backed by over a decade of trusted partnerships developing automotive electronics, mobile communications, and defense applications.

Our Products

At MINRES, we empower engineering teams to build better System-on-Chip (SoC) solutions – faster and with greater confidence.

Flexible, Scalable IP

The Good Folk Series

- Five flexible, scalable RISC-V cores

- Low power for Edge-IoT and embedded

- Available as 32 or 64-bit

- Optimal performance per watt and silicon area

- Trustworthy, generator-based and flexible hardware IP

Hybrid Simulation

VP and RTL running together in parallel

- RAVEN offers more efficient and accurate hardware/software development.

- Faster SystemC simulations through coarse-grained parallelization

- Co-simulation of SystemC and RTL mapped onto FPGA

- On-premise and Cloud

Virtual Prototyping and Platform Modeling

Platform Model

PySysC

written by the customer

MINRES provides VP modeling services for early SW development and architectural exploration. These services are backed by our own environment and open-source libraries. We have a successful track-record with leading semiconductor companies.

- Application logic performing end-user or system-specific functionality. Might be an operating system or a bare-metal application

- Platform model is what we agree with and deliver to the customer. It might be a compiled application or an easy to reconfigure PySysC script.

- Customer provided models can easily be integrated into created platform model

- DBT-RISE as well as QEMU provide open-source high-performance instruction set simulators forming the heart of every platform model. They allow for manifold debug and analysis options

- The open-source SystemC Components Library (SCC) provides frequently used C++, SystemC and TLM components and thus facilitates the creation of VPs.

- SystemC and TLM are Accellera standards for system modeling forming the foundation of our models. They allow for easy reuse of models and composition of platforms.

- C++ builds the foundation of all our system level models. Being proficient in it, we can provide performant and versatile virtual platform models

Insights

Embedding Lifecycle Security to build European Sovereignty in AI and Defense

Embedded system designers today face a security landscape that is broader, more physical, and more time-sensitive than ever before. The ‘traditional’ threats still matter: malware,…

Pipelined RISC-V in RHDL: A Five-Stage Journey Through Hazards and Stalls

At MINRES, we are always trying to find ways to improve hardware design productivity, verification workflows, and system-level integration – and in doing so end…

Implementing ISO 9001 as a small company: why it’s worth it

Choosing to pursue certification to a standard like ISO 9001 can look like a lot of work and an unnecessary burden, particularly to a small…